Download EZmix 2 Full Keygen EZmix is a simple yet powerful mixing and mastering tools which offers access to an array of mix presets including routing, effects, busses and sends. The software gives you an array of mix presets, whether you need to mix vocals, guitars, bass, drums, or keyboards. Toontrack EZmix 2 Crack With Authorization File Download. Toontrack EZmix 2 v2.1.1 Crack is an extremely outstanding software that delivers wondrous output with mixing and mastering options which allow access to an array of mix presets including routing, effects, busses and sends. It is full offline installer standalone setup of Toontrack EZmix 2 Crack mac for 32/64. Toontrack EZmix 2 Free Download Latest Version r2r for MAC OS. It is full offline installer standalone setup of Toontrack EZmix 2 Serial key for macOS. Toontrack EZmix 2 Overview. EZmix is a simple, yet powerful mixing tool that gives you access to a huge. Download ezmix 2.1.1 full crack free. EZmix 2 Full version Keygen is a phenomenal mixing program with plethora of tools that provide the user with all they need to start mastering their music like professionals. It is ideal for mixing vocals, instruments such as drums, bass, synths. Toontrack EZmix 2 crack features so many effects that will drastically enhance your music and make your projects sound much better.

Jun 07, 2012 Re: Vmware Windows 98 Pci System Peripheral Post by Detective » Thu Jun 07, 2012 3:21 am Below you can download vmware windows 98 pci system peripheral driver for Windows. Driver Pci System Peripheral Windows 98 Vmware Fusion Update. 3/19/2017 0 Comments D acceleration in virtual machines - Part 1: VMware & Direct. Pentium Processor to PCI bridge. Go to C: Windows System for the. I didn't worry because I knew Windows 98 had no driver for the sound. Problem installing sound card driver in Windows. Windows 98 vmware player audio drivers. Jul 18, 2013 The ethernet controller uses AMD PCNET drivers - I think they should be on the Windows install disk, but if not, Google may be able to help. The 'PCI System Peripheral' is the VMCI bus device - this does not work on Windows 98, and can be ignored.

The universal shift register is able to operate in all these modes because of the four-to-one multiplexers that supply the flipflops. Our 4-bit universal shift register is built with four blocks each constituted of a 4X1 mux and a D-flipflop.

- Arts

- Business

- Certifications

- Commerce

- Computer Science

- Graphics Designing and Multimedia

- Networking

- Programming Languages

- Earth Sciences

- Engineering

- English

- Formal Sciences

- Health Sciences

- Natural Sciences

- Political Science

- Social Sciences

| <<< Previous | SHIFT REGISTERS: Serial In/Shift Left,Right/Serial Out Operation | Next >>> |

LessonNo. 34

Theneed to storagebinarydatawasdiscussedearlier. In digitalcircuitsmulti-bitdata

has to be storedtemporarilyuntil it is processed. A flip-flop is able to store a singlebinarybit of

information.Multiplebits of dataarestored by usingmultipleflip-flopswhichhavetheirclock

inputsconnectedtogether.Thus, by activatingtheclocksignalmultiple-bits of dataarestored.

Technically, a registerperformstwobasicfunctions. It storesdataand it moves or

shiftsdata.Theshifting of datainvolvesshifting of bitsfromoneflip-flop to theotherwithinthe

register or movingdata in andout of theregister.Theshiftoperation of thebinarydata is

carriedout by applyingclocksignals.Severaldifferentkinds of shiftoperationscan be

identified.Thedifferentshiftoperationsaredescribedusing a 4-bitshiftregister.

Data is shifted in theright-handdirectiononebit at a timewitheachtransition of the

clocksignal.Figure34.1.Thedataenterstheshiftregisterseriallyfromthelefthandsideand

afterfourclocktransitionsthe4-bitregisterhas4-bits of data.Thedata is shiftedoutserially

onebit at a timefromtherighthandside of theregister if clocksignalsarecontinuously

applied.Thusafter 8 clocksignalsthe4-bitdata is completelyshiftedout of theshiftregister.

SerialIn/SerialRight/SerialOutOperation

Data is shifted in theleft-handdirectiononebit at a timewitheachtransition of the

clocksignal.Figure34.2.Thedataenterstheshiftregisterseriallyfromtherighthandsideand

afterfourclocktransitionsthe4-bitregisterhas4-bits of data.Thedata is shiftedoutserially

onebit at a timefromthelefthandside of theregister if clocksignalsarecontinuouslyapplied.

Thusafter 8 clocksignalsthe4-bitdata is completelyshiftedout of theshiftregister.

SerialIn/SerialLeft/SerialOutOperation

TheSerialShiftregisterhasbeendiscussedearlier,implementedusingJ-Kflip-flops.

Serialshiftregisterscan be implementedusinganytype of flip-flops. A serialshiftregister

implementedusing D flip-flopswiththeserialdataapplied at the D input of thefirstflip-flopand

serialdataoutobtained at the Q output of thelastflip-flop is shown.Figure34.3. At eachclock

transition1bit of serialdata is shifted in and at thesameinstant1-bit of serialdata is shifted

out.For a 4-bitshiftregister, 8 clocktransitionsarerequired to shift in 4-bitdataand

CS302 - Digital Logic & Design

completelyshiftoutthe4-bitdata. As thedata is shiftedout1-bit at a time, a logic 0 value is

usuallyshifted in to fill up thevacantbits in theshiftregister.

Figure34.3bTimingdiagram of a SerialIn/ShiftRight/SerialOutRegister

Theshiftleftandshiftrightshiftregistersareidentical in theirworking.Theyare

connecteddifferentlyforshiftleftandshiftrightoperations.BidirectionalShiftRegistersare

availablewhichallowdata to be shiftedleft or right.Figure34.4.The4-bitregister is

configured to shiftleft or right by settingtheRIGHT / LEFTsignal to logichigh or low

respectively.Whentheregister is configured to shiftright,the AND gatesmarked 1 are

enabled.Theinput of thefirstflip-flop is connected to theserialInput,theinputs of thenext

threeflip-flopsareconnected to the Q outputs of thepreviousflip-flops.Thus on a clock

transitiondata is shifted1-bittowardstheright.Theserialdata is shiftedout of theregister

throughoutput Q3. Whentheregister is configured to shiftleftthe AND gatesmarked 2 are

enabled,connectingthe Q outputs of theflip-flop on therighthandside to the D input of the

flip-flop on thelefthandside.Thus on eachclocktransitiondata is shifted1-bittowardsleft.

Serialdateout is availablethroughthe Q0 output.Serialdata is inputthroughtheSerialData in

linewhich is connected to thefourth AND gatemarked 2 on theextremerighthandside.

CS302 - Digital Logic & Design

Serial

2

2

2

2

In

Q3

SET

SET

D

D

Q

Q

Q1

flip-flop 1

flip-flop 3

Q

Q

CLR

CLR

CLK

RIGHT / LEFT

Figure34.4bTimingdiagram of a Bi-directional,4-bitShiftregister

ThetimingdiagramshowstheoperationtheBi-directionalshiftregisterwhichinitiallyshifts

datatowardstheleft. At interval t5, theregistered is configured to shiftrightand at t8 towards

leftandagaintowardstheright at interval t14. A logic 1 is applied at theSerialdatainputfrom

intervals t1 to t10. At interval t11 andonwards a logic 0 is applied at theSerialdatainput.

Data is shifted in theleft-handdirectiononebit at a timewitheachtransition of theclock

signal.Thedataenterstheshiftregisterseriallyfromtherighthandsideandafterfourclock

transitionsthe4-bitregisterhas4-bits of data.Thedata is shiftedout in parallel by the

CS302 - Digital Logic & Design

application of a singleclocksignal.Theshiftregisterhas 4 paralleloutputs.Thecircuit

diagram of theSerialIn/ParallelOutregister is shown.Figure34.5.

SerialIn/ParallelOutOperation

The74HC164 is an MSI 8-bitSerialIn/ParallelOutShiftRegister.TheShiftregister

has 8 parallelOutputs, an AsynchronousActive-lowCLRinputwhichclearstheshiftregister.

Theshiftregister is triggered on thepositiveclocktransition.TheSerialdata is appliedthrough

inputs A and B. Inputpins A and B areinternallyconnectedthrough an internal NAND gate.

Thetwopinsact as a datainputandshiftregisterenableinputs.Serialdata is applied at either

input A or B. Theotherinputwhenset to logichighenablestheshiftoperation.TheFigure

A

74HC164

CLK

Figure34.6a74HC164,8-bitSerialIn/ParallelOutShiftRegister

CS302 - Digital Logic & Design

Figure34.6bTimingdiagram of a 74HC164,8-bitSerialIn/ParallelOutShiftRegister

In thetimingdiagram,theregister is clearedasynchronously by activatingtheactive-

lowCLRinput at interval t0. Theserialdata is applied at input A of theregisterbeforeinterval

t0. However,theregister is enabled to performshiftoperation at interval t1, wheninput B is set

to logichigh. At interval t2, there is a low to hightransition in theserialdatainputwhich is latch

by thefirstflip-flop at thepositiveclocktransition at interval t3. AT eachpositiveclocktransition

frominterval t4 to t10 thedata is shiftedright by 1-bit.

Theregisterhasparallelinputs,databitsareloadedintotheregister in parallel by

activating a loadsignal.Thedata is shiftedoutserially by application of clocksignals.Thus in

a 4-bitshiftregister,after 4 clocksignalsthe4-bitdata is completelyshiftedout of theshift

350

Figure34.7

Theinternalcircuit of a 4-bitParallelIn/SerialOutShiftregister is shown.Figure34.8.

The4-bitdata is initiallyloaded in Parallelintotheshiftregister by settingthe

SHIFT / LOADinput to logiclow.The AND gatesmarked 2 areenabledallowingdata to be

applied at theinputs of therespective D flip-flops. On a positiveclocktransitionthedata is

latched by therespectiveflip-flops. To shiftthedata,theSHIFT / LOADis set to logichigh

whichenables AND gatesmarked 1 connectingthe Q outputs of theeachflip-flopconnected

D0

D2

SHIFT / LOAD

2

2

2

SET

SET

D

D

Q

Q

Q0

Q2

Data

flip-flop 2

flip-flop 4

Q

Q

CLR

CLR

CLK

4-bitParallelIn/SerialOutShiftregister

The74HC165 is an 8-bitParallelIn/SerialOutregisterwhichcanalsowork as an 8-bit

SerialIn/SerialOutregister.TheParallelData is loadedasynchronously by usingthe

AsynchronousSet/ClearInputs.Afterloadingtheparallel8-btidata,theserialshiftoperation is

carriedout by enablingtheclocksignal.TheCLKandCLK INH signalareinternallyconnected

through an OR gate to theclockinputs of theeightflip-flops.Theclocksignal is enabled by

351

D0 D1 D2 D3 D4 D5 D6 D7

Q7

74HC165

Q7

Figure34.9

5. ParallelIn/ParallelOutOperation

Theregisterhasparallelinputsandparalleloutputs.Data is entered in parallel by

applying a singleclockpulse.Data is latched by theflip-flops on theclocktransitionand is

available in parallelform at theflip-flopoutputs.Figure34.10.Theinternalcircuit of 4-bit

ParallelIn/ParallelOutRegister is shown.Figure34.11.TheParallelIn/ParallelOutregister

storesParalleldataandusuallydoesnotallowsanyshiftoperations.

Figure34.11 A D-flip-flopbased4-bitParallelIn/ParallelOutRegister

CS302 - Digital Logic & Design

J

74HC195

CLR

Q0 Q1 Q2 Q3

Figure34.1274HC195,4-bitParallelIn/ParallelOutShiftRegister

The74HC195 is a 4-bitParallelIn/ParallelOutRegister. It alsohas a Serial In input,

thereforetheregistercanalso be used as a SerialIn/ParallelOut or as a SerialIn/SerialOut

register.Theoutput Q3 is used as a SerialOutpin.74HC195.The J andK inputsareused to

inputdataserially.Theseinputsareconnected to thefirstflip-flop.TheSH / LD is used to load

theParallelDataand to allowshiftoperations on theclocktransition.TheCLRinput is used to

D0 D1 D2 D3

S0

74HC194

SL SER

Q0 Q1 Q2 Q3

Figure34.13Bi-directional4-bitUniversalShiftRegister

The74HC194 is a 4-bitBidirectionalShiftregisterthatshiftsdata in theleftandright

handdirectionsandhasbothParallelandSerialinputandoutputcapability.Figure34.13.The

registerhas4-bitParallelInputs D0 to D3 andParallelOutputs Q0 to Q3. An activelow

AsynchronousCLRinputclearstheregister.Theregistershiftsdata on a positiveclock

transition. S0 and S1 inputscontroltheoperation of theregister.When S0 and S1 bothare at

logichigh,theregisterloadsparalleldataapplied at theinputs D0 to D3 on theclocktransition.

CS302 - Digital Logic & Design

3 Bit Przepis

When S0 is high,shiftrightoperation is carriedout,serialdata is enteredthroughthe SR SER

input.When S1 is high,shiftleftoperation is carriedout,serialdata is enteredthroughthe SL

SERinput.Whenboth S0 and S1 arelogiclowtheregister is inhibited.

Theserialoutput of theregister is connected to theserialinput of theregister. By

applyingclockpulsesdata is shiftedright.Thedatashiftedout of theserialoutpin at theright

handside is re-circulatedbackintotheshiftregisterinput at thelefthandside.Thusthedata

Figure34.14RotateRightOperation

Theserialoutput of theregister is connected to theserialinput of theregister. By

applyingclockpulsesdata is shiftedleft.Thedatashiftedout of theserialoutpin at theleft

handside is re-circulatedbackintotheshiftregisterinput at therighthandside.Thusthedata

Figure34.15RotateLeftOperation

Shiftregistercountersarebasically,shiftregistersconnected to performrotateleftand

rotaterightoperations.Whendata is rotatedthrough a registercounter a specificsequence of

states is repeated.Twocommonlyusedregistercounters in digitallogicaretheJohnson

1. JohnsonCounter

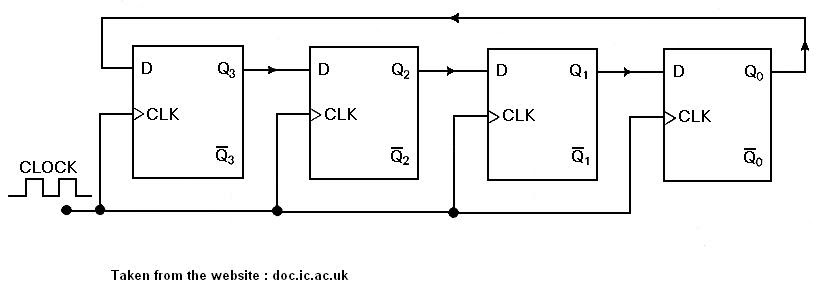

In a Johnsoncounter,theQ output of thelastflip-flop of theshiftregister is connected

to thedatainput of thefirstflip-flop.Thecircuit of a 4-bit, D flip-flopbasedJohnsonCounter is

shown in figure34.16.Thesequence of statesthatareimplemented by a n-bitJohnson

counterare2n.Thus a 4-bitJohnsoncountersequencesthrough 8 statesand a 5-bitJohnson

354

Figure34.164-bitJohnsonCounter

Q0

Q2

Pulse

0

0

1

0

0

1

0

3

1

0

1

1

5

1

1

0

1

7

0

1

Table34.1Sequence of states of a 4-bitJohnsonCounter

TheRingCounter is similar to theJohnsoncounter,exceptthatthe Q output of thelast

flip-flop of theshiftregister is connected to thedatainput of thefirstflip-flop of theshift

register.Alltheflip-flops of thecounterarecleared to logiclowexceptforthefirstflip-flop

PRE

Figure34.174-bitRingCounter

Aftertheinitialization of thecounter,thelogichighset at theoutput of thefirstflip-flop

is shiftedright at eachclocktransition.Table34.2.With a RingCountercircuit no decoding

gatesarerequired.Eachstate of theringcounterhas a uniqueoutput.

Q0

Q2

Pulse

1

0

1

1

0

0

1

3

0

1

355

The following is the VHDL code for 4-bit SIPO in behavioural modelling.

| Source: https://www.ee.usyd.edu.au/tutorials/digital_tutorial/part2/register03.html |

use ieee.std_logic_1164.all;

port( res: in std_logic;

clk: in std_logic;

end sipo;

architecture beh of sipo is

begin

begin

temp<='0000';

temp(3)<=sin;

temp(1)<=temp(2);

end if;

pout<=temp;

USE ieee.std_logic_1164.ALL;

Vhdl Program For 3 Bit Bidirectional Shift Register Of Deeds

END sr;

ARCHITECTURE behavior OF sr IS

--Component Declaration for the Unit Under Test (UUT)

PORT(

sin : IN std_logic;

pout : OUT std_logic_vector(3downto 0)

ENDCOMPONENT;

signal res : std_logic := '0';

signal clk : std_logic := '0';

--Outputs

constant clk_period : time := 50 ns;

BEGIN

uut:sipo PORT MAP (

sin => sin,

pout => pout

clk_process :process

clk<= '0';

clk<= '1';

endprocess;

--Stimulus process

begin

wait for 50 ns;

3 Bit Bidirectional Shift Register

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait for 50 ns;

wait;

END;

Waveform:Vhdl Program For 3 Bit Bidirectional Shift Register Free